반응형

| 1100 && 0101 : 논리 and (이항 연산자) > 0,x,z가 아닌 정해진 값이면 1 , 1 and 1이 되서 값은 1 1100 & 0101 : 비트단위 and > 위치가 같은 비트 끼리 and 연산 , 결과는 0100 & 1100 : 축약 and (단항 연산자) > 모든 비트끼리 and , 1 and 1 and 0 and 0 = 0 |

수식에서 정수형 수의 처리

| integer IntA, IntB, IntC, IntD; IntA = -12 / 4; // The result is -3. IntB = -'d12 / 4; // The result is 1073741821. IntC = -'sd12 / 4; // The result is -3. IntD = -4'sd12 / 4; // -4'sd12 is the negative of the 4-bit 1100, // which is -4. -(-4) = 4. The result is 1. |

산술연산자

- 피연산자의 비트에 x (unknown)나 z (high-impedance)가 포함된 경우에는 전체 결과 값은 x가 됨, ex) 4/ ?(x) = ?(x)

- 나누기와 나머지 연산자에서 두 번째 피연산자가 0인 경우, 결과값은 x가 됨 , ex) 4 / 0 = ?(x)

- 나머지 연산자의 결과 값은 첫번째 피연산자의 부호를 따름 , ex) -8%3 = -2 , 8%-3 = 2

- 거듭제곱 연산자에서 다음의 경우에는 결과 값이 정의되지 않음 >> 첫번째 피연산자가 0이고 두 번째 피연산자가 양수가 아닌 경우 , ex) 0^-2 = ? >> 첫번째 피연산자가 음수이고 두 번째 피연산자가 정수 값이 아닌 경우 , ex) -2^0.5 : 허수

관계연산자

- 산술 연산자보다 낮은 우선 순위를 가짐

- 피연산자의 비트에 x (unknown) x (unknown)나 z(high-impedance) impedance)가 포함된 경우에는 결과 값은 1비트의 x가 됨

- 두 피연산자의 비트 수가 다른 경우에는, 비트 수가 작은 피연산자의 MSB 쪽에 0이 채워져 비트 수가 큰 피연산자에 맞추어진 후, 관계를 판단함

- 피연산자 중 하나가 실수형이면 다른 피연산자가 실수형으로 변환된 후, 비교됨

등가연산자

- 관계 연산자 보다 낮은 우선순위를 가짐

- 피연산자의 비트끼리 비교

- 두 피연산자의 비트 수가 다른 경우에는, 비트 수가 작은 피연산자의 MSB 쪽에 0이 채워져 비트 수가 큰 피연산자에 맞추어진 후, 등가를 판단함

- case equality와 case inequality 연산자( !) ===, !==)는 실제 회로 사용시에는 쓰지 않는게 좋다.

논리연산자

- 참 또는 거짓의 판단이 모호한 경우에는 결과값은 x

- a&&b(and), a||b(or), !a(not)

- 0, x, z 가 아닌경우 논리 값은 1

| A=3, B=0, C=2'b0x, D= 2'b10 //논리 값은 순서대로 1, 0 , x , 1 A&&B // 결과 값은 0 A||B // 결과 값은 1 'A // 결과 값은 0 C&&D // 결과 값은 x |

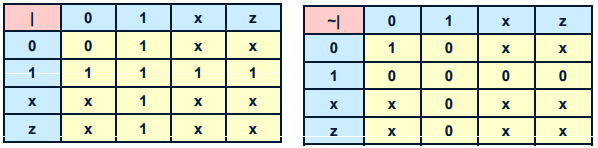

비트연산자

- 피연산자의 해당 비트들에 대한 연산을 수행

- 피연산자의 비트 수가 같지 않으면, 비트 수가 작은 피연산자의 MSB 위치에 0이 채워진 후, 연산됨

축약연산자

- 단항연산자

- 피연산자의 단위 비트들에 적용되어 단일 비트의 결과값을 생성

| reg[7:0] cnt; 1의개수가 홀수인지 짝수인지 알 수 있음 assign parity = ^cnt; assign parity = cnt[7]^cnt[6]^cnt[5]^cnt[4]^cnt[3]^cnt[2]^cnt[1]^cnt[0]; |

시프트 연산자

논리 시프트 연산자 (<<, >>)

- << : 우측 피연산자 값만큼 좌측으로 시프트 후, 비어 있는 비트에 0을 채움

- >> : 우측 피연산자 값만큼 우측으로 시프트 후, 비어 있는 비트에 0을 채움

산술 시프트 연산자 (>>>, <<<)

- <<< : 우측 피연산자 값만큼 좌측으로 시프트 후, 비어 있는 비트에 0을 채움

- >>> : 우측 피연산자 값만큼 우측으로 시프트 후, 비어 있는 비트에 좌측 피연산자의 MSB를 채움

우측 피연산자

- x 또는 z가 포함된 경우, 시프트 연산의 결과 값은 x

- 항상 unsigned 수

| a*3.75 = 3a + 0.75a = a + 2a + 0.5a + 0.25a = a + a<<1 + a>>1 + a>>2 연산이 더 빨라진다. |

| 1110 >>1 : 0111 1110 >>>1 : 1111 빈 부분을 MSB로 채운다 |

조건 연산자

- expression1 이 참(1, 즉 0, x 또는 z가 아닌 값)으로 평가되면 expression2의 값이 좌변의 변수에 할당

- expression1이 거짓(0)으로 평가되면 expression3의 값이 좌변의 변수에 결과 값으로 할당

- expression1이 x 또는 z이면(즉, 참 또는 거짓을 판단할 수 없는 모호성이 존재하는 경우), expression2와 expression3을 함께 평가하여 비트 단위로 비교된 값이 좌변의 변수에 할당 >>expression3이 real 형 값이 아니면 결과 값은 비트 단위로 비교되어 결정되며, real 형 값인 경우에는 결과 값은 0이 됨

| 형식 conditional_expression :: = expression1 ? expression2 : expression3 |

조건 연산자를 이용한 3상태 버퍼

| wire [15:0] busa = drive_busa ? data : 16'bz; 16비트(16가닥) 선 busa에 초기값 할당 drive_busa의 값이 참이면 busa에 data 할당 거짓이면 16'bz 할당 |

결합 연산자

- 중괄호 { }에 의해 묶인 두 개 이상의 표현이 갖는 비트들을 결합 >> 결합되는 피연산자들은 각각의 크기를 결정할 수 있어야 결합이 가능 >> unsized unsized 상수는 결합 연산자로 결합시킬 수 없음

ex

| {a, b[3:0], w , 3'b101} >9bit 독립적으로 분리되어 있는 데이터를 하나로 묶는 것 결과 {a, b[3], b[2], b[1], b[0], w, 1'b1, 1'b0, 1'b1} >9bit |

- 대입문의 좌측 또는 우측에 사용 가능

- 비트 폭이 일치하지 않는 변수의 연산이나 대입이 허용됨 >> 우변의 비트 폭이 작은 경우, 우변의 MSB에 0을 붙여 연산 됨 >> 좌변의 비트 폭이 우변 보다 작을 경우, MSB는 누락되어 저장

| wire [15:0] addr_bus; assign addr_bus = {addr_hi, addr_lo}; // addr_hi, addr_lo는 8비트 신호 |

| wire [3:0] a, b, sum; //4비트 선 a,b,sum wire carry; //1비트 선 carry assign {carry, sum} = a + b; // 4비트 데이터의 덧셈은 5비트 결과 // 좌변이 5 비트이므로, 우변의 a+b는 MSB에 0을 붙인 5비트로 연산 됨 |

반복 연산자

- {a{b}} 의 형태로 표현하여 b를 a회 반복 >> 반복 횟수 a는 0, x, z가 아닌 상수이어야 함

ex)

| {4{w}} // {w, w, w, w}와 동일한 표현. a[31:0] = {1'b1, {0{1'b0}} }; // 우변이 {1'b1}가 되므로 잘못된 표현임. > 반복횟수가 0 a[31:0] = {1'b1, {1'bz{1'b0}} }; // 우변이 {1'b1}가 되므로 잘못된 표현임. > 반복횟수가 z a[31:0] = {1'b1, {1'bx{1'b0}} }; // 우변이 {1'b1}가 되므로 잘못된 표현임. > 반복횟수가 x |

| result = {func(w), func(w), func(w), func(w)}; result = {4{func(w)}}; // 위의 문장과 동일함. {b, {3{a, b}}} // {b, a, b, a, b, a, b}와 동일함. |

반응형

'study > Logic Circuit' 카테고리의 다른 글

| 할당문 (0) | 2020.10.25 |

|---|---|

| 게이트 수준 Modeling (0) | 2020.10.10 |

| Verilog 자료형 (0) | 2020.10.08 |

| Verilog HDL 개요 , 회로설계 모델링, 어휘 규칙 (0) | 2020.10.07 |

| 기본 (0) | 2020.10.07 |